# GLOBAL JOURNAL OF ENGINEERING SCIENCE AND RESEARCHES HIGH PERFORMANCE FIR FILTER USING BOOSTED CMOS DIFFERENTIAL LOGIC STYLE

# Ritu Juneja, Sandeep Khantwal

School Of Engineering & Technology, Ganga Technical Campus, Soldha, Bahadurgarh

#### ABSTRACT

This paper describes a high performance FIR filter using boosted CMOS differential logic style. speed boosted CMOS differential logic which is used in ripple carry adders. The proposed logic style improves switching speed by boosting the gate–source voltage of transistors along timing-critical signal paths. Test sets of logic gates were designed in a 0.18-µm CMOS process, whose comparison results indicated that the energy–delay product of the proposed logic style was improved when compared with conventional logic styles at supply voltage of 1.8V. The experimental result for an FIR filter using the proposed logic style revealed that the addition time is reduced as compared with the conventional logic style.

Keywords-. Adder, Low Power, Low Voltage, Voltage Boosting, Addition Time.

#### Introduction

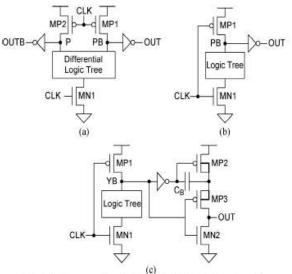

Bootstrapping is an effective method for speed improvement and power reduction. One of the famous methods to decrease the power consumed by a CMOS digital circuit is scaling of supply voltage. This is due to the fact that the switching power consumed by the circuit has a quadratic relationship with supply voltage. In certain cases, the circuit is made in a way to operate in the sub threshold region for achieving maximum energy efficiency. However this idea is restricted and used in a design of low end where speed is taken as the secondary concern due to severe speed degradation because of small switch current and variability of high performance due to the variations in process, temperature and threshold voltage. For designing a medium and high end in which performance of the speed and energy efficiency both gets importance, no acceptance of large aggressive scaling of voltage and then a close threshold voltage design is more accurate for gaining relatively high energy efficiency in the absence of severe speed degradation. The method of voltage scaling helps in reducing the total power consumption of a system. In applications where high speed is necessary differential cascade voltage switch is neglected due to the insufficient speed of the circuit. Furthermore, domino logic is not suitable due to the reduction of overdrive voltage. As the scaling of supply voltage approaches the threshold voltage the performance of the speed of previous CMOS circuits like logic of static CMOS, logic of the differential cascade voltage switch (DCVS) [see Fig. 1(a)] and logic of the domino CMOS [see Fig. 1(b)] is degraded due to the reduction in overdrive voltage (VGS - VTH) of transistors. To eliminate this problem, a bootstrapped CMOS containing large capacitive load driver was suggested. It was a solution to problem of speed degradation. It can enhance the switching speed at supply voltage which is low by giving the voltage of some inherent nodes goes boosted beyond the supply rails. In this two capacitors are utilize for the purpose of bootstrapping. However this circuit was suggested for used as a driver of large capacitive load, logic fuctions cannot be effectively fit into the circuit and the benefits of speed was not completely exploited. For the operation of fast logic with low supply voltage, BDL known as CMOS bootstrapped dynamic logic was suggested [see Fig.1(c)]. However, the speed of this BDL was not improved too much due to the latent bulky bootstrapped circuit which was superimposed over the entire latency of the circuit. Moreover, there is a restriction of composition of logic of this BDL since it is referred as a one ended structure.

ISSN 2348 - 8034 Impact Factor- 4.022

Fig. 1. Conventional digital CMOS circuits. (a) DCVS. (b) Domino CMOS logic. (c) BDL.

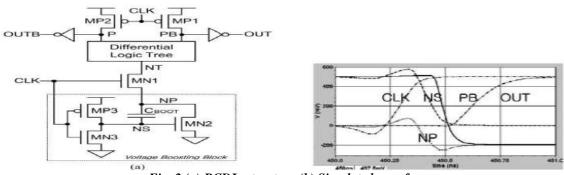

To overcome the above problem BCDL differential logic style was suggested. It is not only better in terms of improving switching speed but also reduces area due to sharing of single boosting circuit. Switching speed is better due to the boosting of overdrive voltage along the path of critical timing signal. Furthermore the problem of latency can be removed by allowing the block of voltage boosting directly to the tree of differential logic.

It contains a differential logic block referred as precharged and a voltage boosting block. The lower part of the circuit is known as voltage-boosting block, which is given in the dotted box consists of transistors known as MN2, MN3, and MP3 and CBOOT referred as boosting capacitor and is utilized in boosting of the voltage of NP approaches below the ground. The logic block known as precharged differential, which is made of a tree of differential logic with bottom transistor namely MN1, precharge transistors known as MP1 and MP2 and output inverters receives the boosted voltage at NP and evaluates the value of the output logic. Its operation is taking place in two phases known as a precharge phase and a phase of boosted evaluation. The circuit follows precharge phase when the value of CLK is low. During precharge phase, separation of the precharge differential logic block from the block of voltage boosting takes placed due to the turn of MN1. Precharge nodes known as P and PB that are in the differential logic block are precharged to the supply voltage with the help of MP1 and MP2 resulting in outputs namely OUT and OUTB low. During the similar time, turn on of the transistors referred as MP3 and MN2 in the block of voltage boosting takes place resulting NS to be high and NP to be low. Then a voltage that is similar to the supply voltage is applied to CBOOT. When CLK changes from low to high then the circuit comes into the boosted evaluation phase. The executed

# ISSN 2348 - 8034 Impact Factor- 4.022

waveforms in this phase of BCDL are shown in Fig. in which utilization of supply voltage of 0.5V is used. When CLK rises to high then turn on of MN1 takes place and connection of the differential logic tree to the block of voltage boosting block is operated. During this time pull down of NS takes place toward the ground result in boosting of NP and NT below the ground with the help of capacitive coupling carried through CBOOT. As given in Fig. , NP temporary reach at -250 mV and settles at near -200 mV by the action of boosting. Then the MN1 gate to source voltage and transistors that are in the logic in driving strength of all these transistors. However, a little forward in the voltage of source body established in these transistors using boosting source voltages approaches below the ground. Meanwhile, the boosted voltage appearing at NT is then goes to P or PB is pulled down below the ground. Then, there is an enlargement in the gate source voltage of the driver PMOS transistor increases its driving strength. Effects of all these driving strength carried out by boosting are then combined together along the path of timing critical signal taken from input to output through nodes of precharging that results in improvement of switching speed at a region of low voltage.

## **BCDL FIR FILTER**

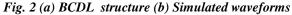

Using logic of BCDL, FIR filter can be designed. It contains adder, deay element and array multipliers. Fig.5.10 shown below is a BCDL logic FIR filter.

Fig.3. BCDL logic FIR FILTER

In place of h (0), h (1), h (2)......h (4) array multiplier is implemented. These structures use many multipliers and adders. Because this work is focused on reducing size and power consumption of a FIR filter.

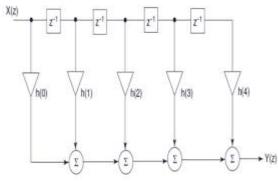

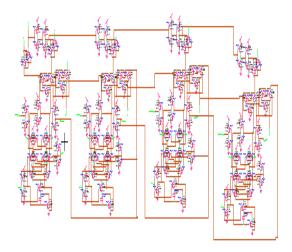

Fig.4 Transistor level structure of previous BCDL FIR Filter

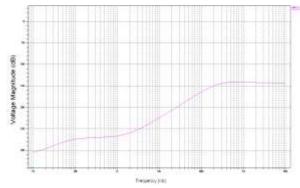

Fig.5 Frequency response of conventional BCDL FIR filter

# **EXPERIMENT RESULTS**

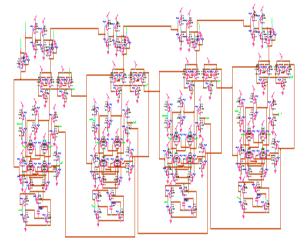

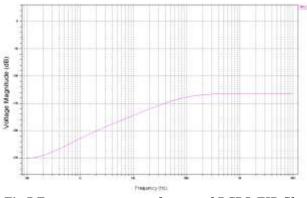

The experimental result is carried out for an FIR filter using the BCDL full adder, array multiplier and delay elements. Transistor level structure of proposed BCDL FIR filter is shown in fig.6 and its frequency response is shown in fig.7

Fig.6. Transistor level structure of proposed BCDL FIR filter

Fig.7 Frequency response of proposed BCDL FIR filter

| TYPES OF FILTER                 | POWER<br>CONSUMPTION(ns) | ADDITION TIME ( 28 ) | POWER DELAY<br>PRODUCT(PDP)(ns*<br>ns) |

|---------------------------------|--------------------------|----------------------|----------------------------------------|

| BCDL FIR FLTER<br>(PROPOSED)    | 16.69                    | 10.05                | 298.58                                 |

| CONVENTIONAL<br>BCDL FIR FILTER | 33.49                    | 70.05                | 424.15                                 |

### Table 1. Comparisons of previous and proposed BCDL FIR filter

### CONCLUSION

CMOS differential logic style with feature of voltage boosting has been described. The BCDL gives better switching speed when compared to conventional logic style at low supply voltage by using a single boosting circuit that is shared by complementary outputs. The BCDL also reduces the area. Comparison results in a tsmc 0.180 um cmos process shows that the energy delay product of the recommended BCDL FIR filter was improved when compared with the conventional BCDL FIR filter. The experiment result for proposed BCDL FIR filter using BCDL logic style indicated a reduction in the addition time.

#### REFERENCES

- [1] P. Chandrakasan, S. Sheng and R. W. Broderson, "Low power CMOS digital design", IEEE J. solid state circuits, vol.27, no.4, pp. 473-483, Apr.1992.

- [2] Reto Zimmermann and Wolf Gang Fichtner, "Low power logic styles CMOS versus Pass Transistor Logic," IEEE Journal of solid state circuits, vol.32, no.7 July 1997.

- [3] C. Piguet, J. M. Masgonty, P. Mosh, C. Arm and V. Von. Kaenel, "Low power low voltage standard cell libraries", in Proc. Low voltage low power workshop, ESSCIRC 95, Lille, France, Sept 1995.

- [4] R. Rogenmoser, H. Kaeslin and N. Felber, "The impact of transistor sizing on power efficiency in sub micron CMOS circuits", in Proc.22nd European Solid State Circuits Conf., Nenchatel, Switzerland, pp. 124-127, Sep 1996.

- [5] C. Piguet, J. M. Magonty, S. Cserveny and E. Dijkstra, "Low power low voltage digital CMOS cell design", in Proc. Patmos 94, Barcelona, Spain, pp.132-139, Oct 1994.

- [6] Noohkubo et al, "A 4.4 ns CMOS 54x54 b multiplier using pass transistor multiplexer", IEEE J. Solid state circuits, vol. 30, pp. 251-257, Mar. 1995.

- [7] P. Ng, P. T. Balsara and D. Steiss, "Performance of CMOS differential circuits", IEEE J. Solid state circuits, vol.30, pp.251-257, Mar 1995.

- [8] K. Chu and D. Pulfrey, "A comparison of CMOS circuit techniques: Differential cascade voltage switch logic versus conventional logic", IEEE J. Solid State circuits, vol.22, pp.528-532, Aug 1987.

- [9] W. Shockley, "A uni-polar field effect transistor," Proc. IRE, vol. 40, pp. 1365-13

- [10] T. Sakurai and A. R. Newton, "Alpha power low MOSFET model and its applications to CMOS inverter delay and other formulas", IEEE Journal of Solid State Circuits, vol.25, pp.584-594, Apr.1990.

- [11] Wang A and Chandrakasan A, "A 180 mV FFT processor using subthreshold circuit techniques" in Proc. IEEE ISSCC, 2004, pp. 292–295.

- [12] Jong-Woo Kim, Joo-Seong Kim and Bai-Sun kong "Low-Voltage Approaching Device Threshold" IEEE Transaction on circuit and System-II Express briefs, Vol.59, no.3, March 2012.